Próxima Geração de Microarquitetura da Intel

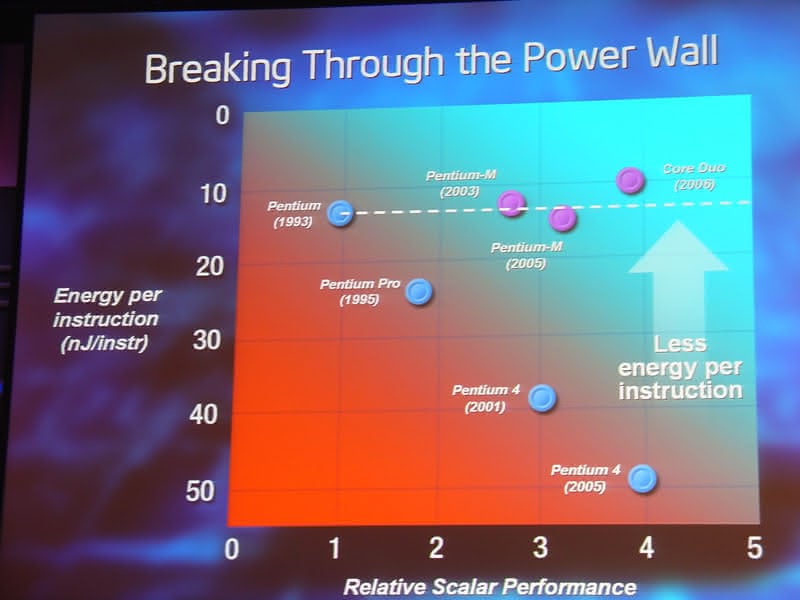

Neste IDF nós pudemos obter mais informações sobre a nova microarquitetura que será usada em todos os novos processadores da Intel a partir do segundo semestre de 2006 e que foi desenvolvida pela equipe de Haifa. Como mencionamos, esta microarquitetura é baseada na do Pentium M e não na do Pentium 4. Esta será a oitava geração de microarquitetura x86 da Intel.

Primeiro, esta nova microarquitetura usa um pipeline de 14 estágios, contra os 21 estágios usados pelo Pentium 4 contra os 30 estágios usados no Pentium 4 “Prescott”. Desta forma, esta nova microarquitetura é mais parecida com processadores Intel de sexta geração, como o Pentium III, do que com processadores Intel de sétima geração.

Ela terá quatro unidades de envio, contra três usadas no Pentium 4. Isso permitirá que o processador envie mais microinstruções por vez para suas unidades de execução, o que obviamente aumenta o desempenho do processador.

Na parte de cache, ela usará um cache L2 compartilhados com todos os núcleos do processador, como o Yonah. Isto foi feito para diminuir a taxa de erro do cache, isto é, diminuir a quantidade de vezes em que o cache “acaba” e o processador precisa buscar dados na lenta memória RAM. Com um cache L2 compartilhado entre todos os núcleos do processador, o processador pode dar mais ou menos memória cache L2 para cada núcleo dinamicamente, dependendo da demanda. Em processadores de núcleo duplo com caches separados, se o cache de um núcleo “acaba”, ele precisa buscar dados diretamente na memória, mesmo se o cache L2 do outro núcleo estiver “vazio”. No modelo compartilhado, se o processador tem 2 MB de cache L2 um núcleo pode, por exemplo, usar 1,5 MB e o outro 0,5 MB, diminuindo o número de vezes em que o processador precisa ir à memória RAM buscar dados, aumentando o desempenho.

A Intel está também prometendo que os caches de memória L1 de cada núcleo poderão se comunicar diretamente, e também uma maior taxa de transferência entre o núcleo do processador e o cache de memória L2.

Outra novidade desta nova microarquitetura será um novo conjunto de instruções multimídia (SSE4?), o quinto conjunto de instruções multimídia desde que o MMX foi lançado em 1996.

Todos os processadores terão as extensões de endereçamento de 64 bits, EM64T.

As diferenças entre o Merom, voltado para o mercado de portáteis, o Conroe, voltado para o mercado de desktops, e o Woodcrest, voltado ao mercado de servidores, serão basicamente o tamanho da memória cache L2, o tamanho do TLB (Translation Look-aside Buffer) e a quantidade de memória RAM que o processador consegue acessar. TLB é uma tabela usada pelo sistema de memória virtual (também conhecido como arquivo de troca) que lista o endereço físico de um bloco de endereços associado a cada bloco de endereços virtuais.

Respostas recomendadas

Não há comentários para mostrar.

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora