Introdução

Sandy Bridge é o nome da nova microarquitetura que a Intel usará em seus processadores a partir de 2011. Ela é uma evolução da microarquitetura Nehalem, que foi introduzida com os processadores Core i7 e também usada nos processadores Core i5 e Core i3.

Vamos fazer uma rápida revisão para caso você não acompanhe o mercado de processadores de perto. Após o Pentium 4, que era baseada na microarquitetura de 7ª geração da Intel, chamada Netburst, a Intel decidiu voltar para sua microarquitetura de 6ª geração (a mesma usada nos processadores Pentium Pro, Pentium II e Pentium III, chamada P6), que provou ser mais eficiente. A partir do processador Pentium M (que é um processador Intel de 6ª geração), a Intel desenvolveu a arquitetura Core, que foi usada nos processadores da série Core 2 (Core 2 Duo, Core 2 Quad, etc). Em seguida, a Intel pegou esta arquitetura, melhorou (a principal inovação foi a adição de um controlador de memória integrado) e lançou a microarquitetura Nehalem, que foi usada nos processadores das séries Core i3, Core i5 e Core i7. Tendo como base a microarquitetura Nehalem, a Intel desenvolveu a microarquitetura Sandy Bridge, que será usada em sua nova geração de processadores Core i3, Core i5 e Core i7 lançados em 2011 e 2012.

Para uma melhor compreensão deste tutorial, nós sugerimos a leitura dos tutoriais abaixo, na seguinte ordem:

- Por Dentro da Arquitetura do Pentium M

- Por Dentro da Microarquitetura Intel Core

- Por Dentro da Microarquitetura Nehalem

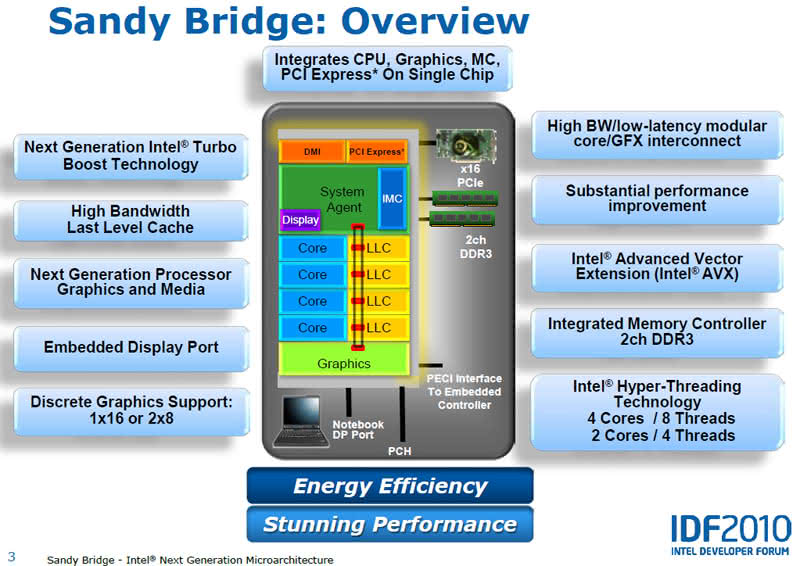

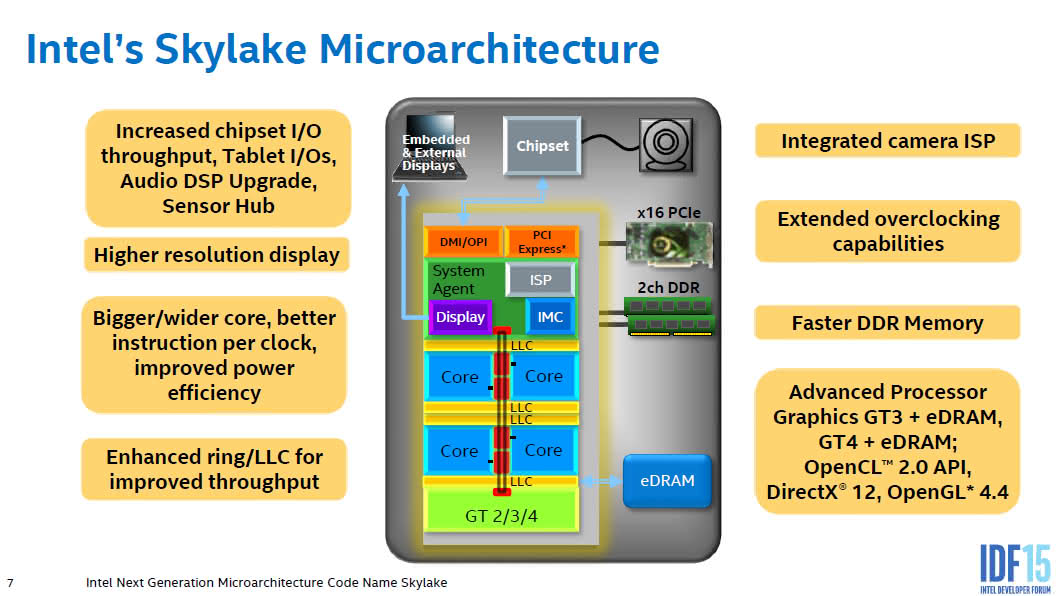

As principais características da microarquitetura Sandy Bridge estão resumidas abaixo. Nós explicaremos cada uma delas em mais detalhes nas próximas páginas.

- A ponte norte (controlador de memória, controlador de vídeo e controlador PCI Express) está integrada no mesmo chip do processador. Nos processadores baseados na microarquitetura Nehalem, a ponte norte está localizada no mesmo encapsulamento do processador, mas em uma pastilha de silício separada. Inclusive nos processadores Nehalem de 32 nm o chip ponte norte é fabricado com processo de 45 nm.

- Os primeiros modelos serão fabricados com tecnologia de 32 nm

- Arquitetura em anel

- Novo cache de microinstruções decodificadas (cache L0, capaz de armazenar 1.536 microinstruções, o que equivale a mais ou menos 6 kB)

- Cache L1 de instruções de 32 kB e cache L1 de dados de 32 kB por núcleo (nenhuma mudança em relação à arquitetura Nehalem)

- O cache de memória L2 foi renomeado para “cache intermediário” (MLC, Mid-Level Cache) com 256 kB por núcleo

- O cache L3 agora é chamado “cache de último nível” (LLC, Last Level Cache) e não é mais unificado, e é compartilhado entre os núcleos do processador e o processador gráfico

- Nova geração da tecnologia Turbo Boost

- Novo conjunto de instruções AVX (Advanced Vector Extensions ou Extensões de Vetor Avançadas)

- Controlador de vídeo aprimorado

- Controlador de memória DDR3 de dois canais redesenhado, suportando memórias até DDR3-1333

- Controlador de memória PCI Express integrado suportando uma pista x16 e duas pistas x8 (nenhuma mudança em relação à arquitetura Nehalem)

- Os primeiros modelos utilizarão um novo soquete com 1155 pinos

Figura 1: Resumo da microarquitetura Sandy Bridge

.thumb.jpg.056c5820338a77d56b819f82e00f5f11.jpg)

14_56.50_37f27dc0.thumb.jpg.7bcd3f6d0862d5bdd3b8eda40d7623cd.jpg)

Respostas recomendadas

Crie uma conta ou entre para comentar

Você precisa ser um usuário para fazer um comentário

Criar uma conta

Crie uma nova conta em nossa comunidade. É fácil!

Crie uma nova contaEntrar

Já tem uma conta? Faça o login.

Entrar agora